PCB從傳統封裝到先進封裝

TO

TO(晶體管外形)是一種電晶體封裝,旨在允許引線模製並用於表面安裝。它主要由塑膠和金屬製成。隨著電晶體應用的進步,TO封裝技術也得到了快速發展。

TO 封裝由 TO 基座和 TO 帽組成。 TO底座作為基礎,為封裝組件提供電源,而蓋子則有利於光訊號的順利傳輸。這兩個元件一起形成一個密封封裝,保護敏感的半導體元件。

DIP

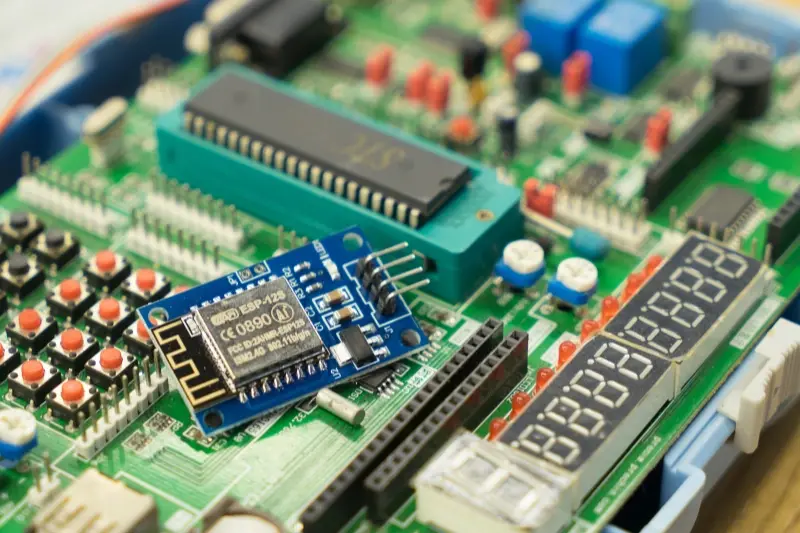

DIP(雙列直插式封裝)是一種引腳數少於 100 個的封裝形式,適合 PCB 上的通孔焊接,操作簡單。 DIP封裝的引腳從兩側延伸出來,使其可以直接焊接到特定結構的晶片插座中或焊接到具有相同孔數的焊盤中。它的主要優點是PCB過孔和焊接的方便性,以及與主機板更好的兼容性。 DIP封裝的材料通常是塑膠或陶瓷。

QFP

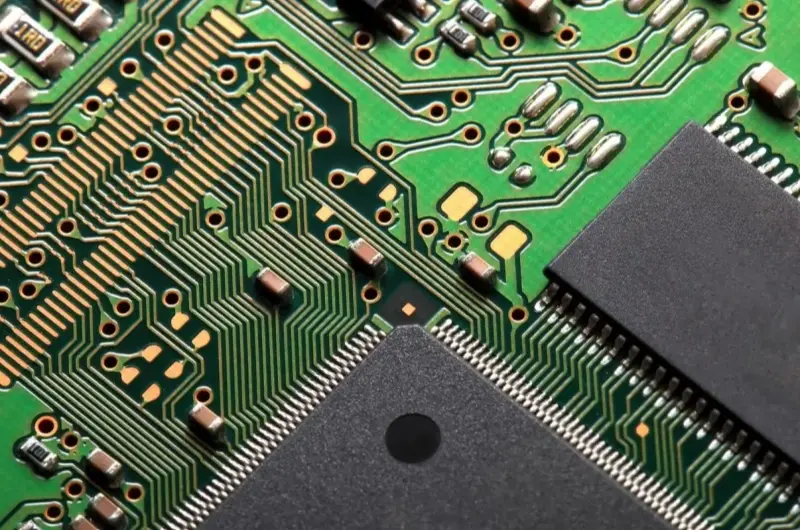

QFP(Quad Flat Package)是一種採用QFP技術的封裝,引腳之間的距離很小,而且引腳很細,一般數量在100個以上。 QFP必須使用SMT(表面貼裝技術)將晶片焊接到主機板上。採用SMT,無需在主機板上鑽孔。主機板表面預先設計了相應的焊點,將晶片引腳與焊點對齊即可確保焊接成功。目前QFP應用廣泛,許多MCU晶片都採用這種封裝。

SOP

SOP(小外形封裝)是一種常見的元件形式,也是表面黏著封裝的一種。其特點是引線從封裝兩側呈海鷗翼形(L形)延伸。常見的包裝材料包括塑膠、陶瓷、玻璃和金屬,其中塑膠是主要材料。 SOP包裝起源於1970年代末期。飛利浦於 1968 年至 1969 年開發了小型外形封裝 SOP。 SOP封裝廣泛應用,衍生出TSOP(薄型小外形封裝)、VSOP(超小外形封裝)、SSOP(收縮小外形封裝)等封裝類型。

BGA

BGA(球柵陣列)是將圓形或柱狀焊球隱藏在封裝下方的封裝。 1990年代後,隨著整合技術的進步,BGA技術迅速發展。目前,高密度、高性能、高頻的IC晶片已採用此封裝技術。 BGA焊接引起了極大的關注,特別是在OEM電子工廠的製造過程中。 OEM工廠的製造能力很大程度取決於BGA焊接品質。

機芯

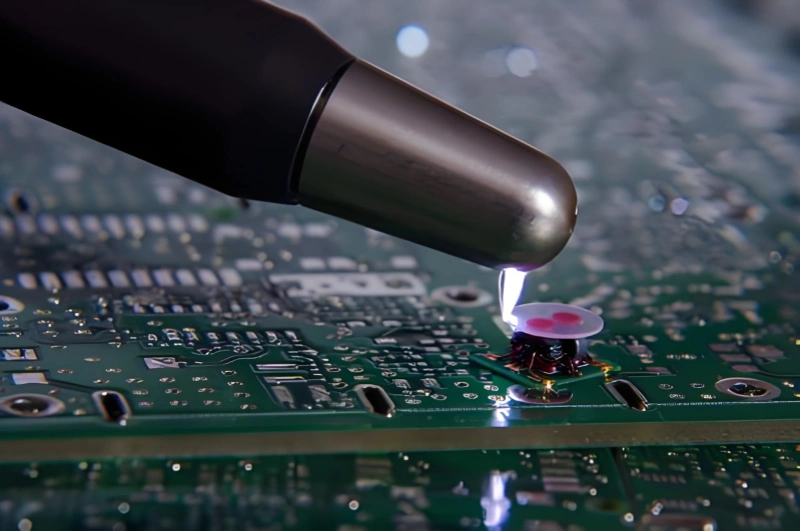

COB(Chip On Board)是一種先進的積體電路封裝技術,將裸晶片直接安裝在印刷電路板(PCB)上,並透過引線鍵合進行電力連接。然後使用環氧樹脂等材料封裝晶片以對其進行保護。這種封裝方式因其尺寸緊湊、性能高、可靠性強而廣泛應用於汽車電子、醫療器材、消費性電子產品等領域。

CSP

CSP(Chip Size Package)是一種先進的封裝形式,封裝尺寸不超過裸晶片尺寸的1.2倍。 CSP技術確保超大規模積體電路以最小的尺寸封裝,在保持高性能和可靠性的同時最大限度地降低成本。與 QFP 和 BGA 相比,CSP 的封裝尺寸顯著減小,預計將成為需要最小尺寸的便攜式產品的首選封裝形式。

WLP

WLP(晶圓級封裝)涉及封裝整個晶圓並在將其切割成單一晶片之前對其進行測試。封裝後的晶片尺寸與裸晶片相同。 WLP 允許使用傳統 SMT 製程將 IC 面朝下安裝在 PCB 上。 IC焊盤使用獨立的焊球直接焊接到PCB焊盤上。 WLP 技術提供小封裝尺寸、IC 和 PCB 之間的低電感以及短生產週期。

2.5D包裝

2.5D 封裝涉及在共享基板上組裝多個 IC 晶片,通常使用矽或有機中介層來互連晶片並將其連接到外部電路。這種封裝技術有助於增強晶片效能並降低功耗。

3D包裝

3D封裝指的是元件不僅在XY平面上排列,而且在垂直Z方向上排列。減少互連長度,有效利用三維空間,提高封裝密度,減少體積,節省材料。

鈷沃斯

CoWoS(Chip On Wafer On Substrate)是一種2.5D整合技術,將不同的晶片堆疊在同一個矽中介層上進行互連。 CoWoS 製程允許晶片連接到晶圓,然後連接到基板,提供高互連密度。

信息

InFO(整合式扇出)是台積電開發的 CoWoS 的廉價版本,它用聚醯胺薄膜材料取代矽中介層,降低了單位成本和封裝高度。該技術在行動應用和高效能運算 (HPC) 市場中廣受歡迎。

系統晶片

SoIC(整合晶片系統)是台積電開發的創新封裝技術,結合了CoWoS和多晶圓堆疊(WoW)。它採用無凸點鍵結結構,可提供更高的凸點密度、更快的速度、更好的性能和更低的能耗。

電磁干擾

EMIB(嵌入式多晶片互連橋)是Intel在2.5D IC封裝上的嘗試。它不需要額外的矽中介層,而是用一個小的矽橋層連接晶片。 EMIB 允許高互連密度、更低的功耗和更高的頻寬。

Foveros 和混合鍵合

Foveros是英特爾的3D封裝技術,可實現不同邏輯晶片的堆疊和連接,結合各種技術、架構和記憶體模組。混合鍵合允許使用混合製程模組進行先進的 3D 封裝,並實現更靈活、高效的解決方案。