High-Speed USB Design on a Two-Layer PCB

In our previous article, “Experience Formulas in PCB Design” we introduced some practical formulas. Now, let’s dive into a real-world application by focusing on high-speed USB design on a two-layer PCB. Typically, designing large-scale high-speed digital signal circuits on a two-layer PCB is not advisable due to its limitations. However, two-layer PCBs are cost-effective, making them a popular choice for personal DIY projects where EMC certification might not be a concern. By following some key guidelines, it’s possible to design high-speed digital circuits like USB, SPI, and Ethernet interfaces on a two-layer PCB. This article will serve as a practical summary of the experience formulas previously discussed.

Handling High-Speed Digital Signals on a Two-Layer PCB

When dealing with high-speed digital signals on a two-layer PCB, two primary principles should be followed: keep traces as short as possible, ideally less than one-tenth of the signal wavelength, and design traces as transmission lines with controlled impedance. Let’s first examine the board’s parameters. Consider a typical 1.6mm thick PCB, with 1oz copper foil, FR-4 dielectric material, and a dielectric constant of 4.6-4.8, with a core thickness of 1.5mm. Using these parameters, we can calculate the signal propagation speed on the PCB. The result shows that the signal propagation distance is approximately 14cm per nanosecond.

Routing USB 2.0 Differential Signal Traces

Next, let’s calculate the trace length on a two-layer PCB to determine if impedance matching is necessary. First, we look at the parameters for USB 2.0 differential signal traces. USB 2.0 operates in three speed modes:

- Low-Speed Mode: Data rate is 1.5Mbps with a rise/fall time of 75-300 nanoseconds (10%-90%). Using the minimum rise time of 75ns, the critical trace length is calculated to be 1 meter. In low-speed mode, traces can be routed like regular signal traces without special considerations.

- Full-Speed Mode: Data rate is 12Mbps with a rise/fall time of 4-20 nanoseconds. Using the minimum rise time of 4ns, the critical trace length is 5.6cm, or 14cm if considering a quarter-wavelength. In full-speed mode, as long as the trace length does not exceed 15cm, impedance matching is generally not required. Additionally, most USB controllers have a tolerance for signals that exceed specifications, so standard PCBs should not face significant impedance issues.

- High-Speed Mode: Data rate is 480Mbps with a rise/fall time of 500 picoseconds. The critical trace length is 7mm or 17.5mm when considering a quarter-wavelength. In this mode, controlling the PCB trace impedance becomes crucial because even short traces approach the signal wavelength.

Preparation Before Routing

Before starting the routing process, it’s essential to calculate the trace width and spacing based on the PCB parameters and ensure proper ground plane placement. For USB 2.0, the D- and D+ data lines form a differential pair with a target differential impedance of 90 ohms. The trace width and spacing must be calculated according to the board’s specifications before routing.

Challenges with USB 3.0 and Differential Pair Length Matching

USB 3.0 has a data rate of up to 5Gbps, which makes it impractical to implement on a two-layer PCB. Additionally, USB 2.0 specifies a differential pair length matching tolerance of 100ps, translating to a length difference of about 1.4cm. Based on these parameters, the trace width and spacing requirements need to be calculated. When using impedance calculation software for a two-layer PCB’s microstrip lines and differential impedance, you’ll find that impedance depends on trace width, spacing, and board thickness.

For a given target impedance, several width-spacing combinations are possible. For example, on a 40mils thick two-layer PCB, a 5mils spacing with a 16mils width might be the optimal choice for better impedance control.

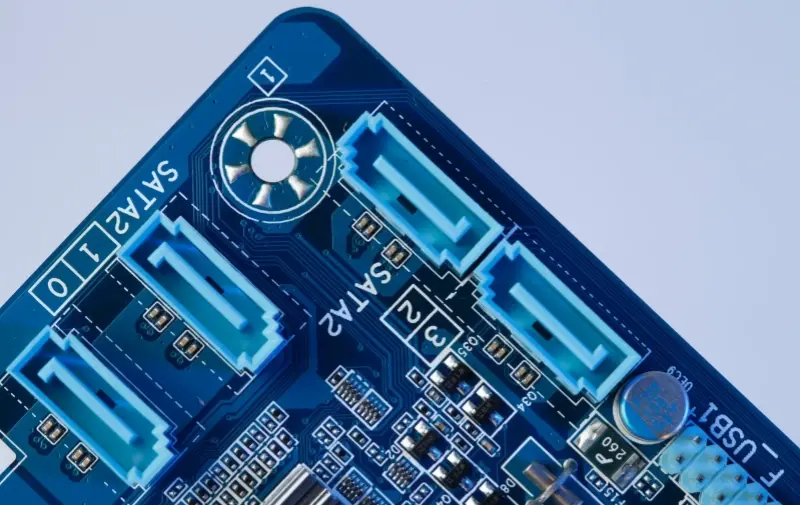

Case Study in Double-sided Board Design

Finally, let’s look at a real case: the design of a 4-port USB 2.0 hub circuit using the MicroChip USB2514 chip, which employs a double-sided board. In this design, the USB differential data lines have parameters of 27 mils in width and 5 mils in spacing, with copper laid under the differential pair, five times the spacing width, which is 25 mils. The distance between the differential pair and other traces should also be kept at least 25 mils. As seen in the PCB layout, near the IC, the width could not be maintained at 27 mils and was reduced to 7 mils, which might cause some impedance discontinuity, so this 7 mil section should be kept as short as possible.

Conclusion

Through this analysis, we see that while designing USB 2.0 on a two-layer PCB presents certain challenges, it is feasible with careful calculation and design. However, implementing higher-speed USB 3.0 on a two-layer PCB is more restricted and may require advanced materials and design techniques. Finally, these experience-based guidelines can also be applied to other high-speed digital interfaces, such as SPI and Ethernet, to ensure optimal circuit performance across various applications.

Related Posts

PCBA Prototype

March 10, 2026

PCBA Prototype

March 7, 2026